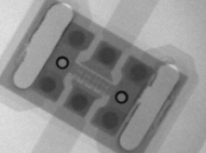

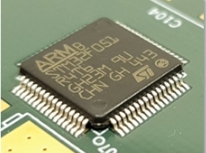

バーティカルチップボンディング例

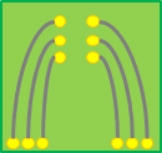

Vertical Flip Chip Bonding

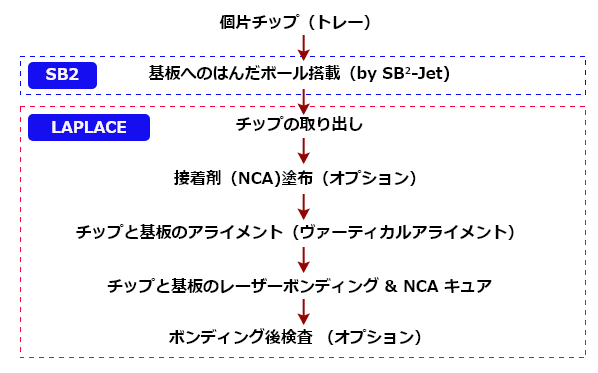

プロセス例(バーティカルチップアセンブリー)

バーティカル ボンディング プロセスフロー

Flip Chip実装用装置:LAPLACE-FC

- 消費エネルギーや発熱を削減

- 小パッケージ化や新たな実装構造を実現

- 光通信デバイスのような複雑な構造にも対応

- 光信号から電気信号への変換を短距離で実現

Flip Chip実装用装置:LAPLACE-FC

アプリケーション:Chipのリワーク

- Laserによる局所加熱と吸引により選択的にChip回収が可能

- さらに局所的に実装&リフロー可能

- ハイエンドWafer Level Pavkage:Fan Out、Embedded、WLCSP など

- 不良Chipのリワーク (回収&実装)

Flip Chip実装用装置:LAPLACE-FC

アプリケーション:極小チップ~大チップ

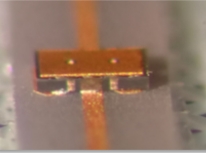

Ultra Small Die Pick-and-Place

and placement on LTCC

(0.35 x 0.55mm die size)

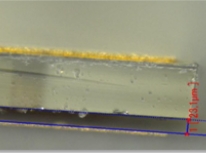

stand-off bump height

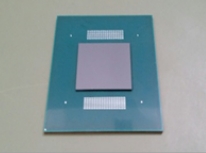

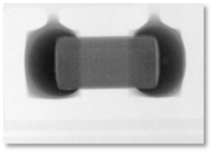

Large Die Placement and In-situ Reflow

(30µm Cu pillar)

Flip Chip実装用装置:LAPLACE-FC

アプリケーション:極小チップ~大チップ

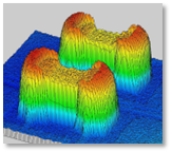

キャパシタ実装

強固なハンダ接合

Surface Mount Technology用装置:LAPLACE-Cap

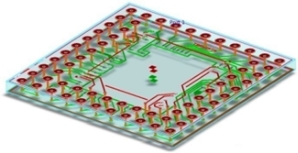

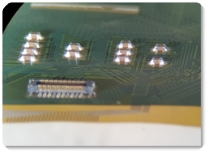

アプリケーションとデバイス:Probe Card

(キャパシタとコネクタ拡大)

(キャパシタとコネクタ拡大)

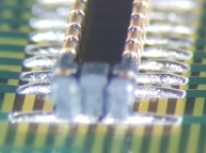

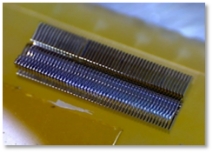

Surface Mount Technology用装置:LAPLACE-Can

アプリケーションとデバイス

(ピッチ:80μm)

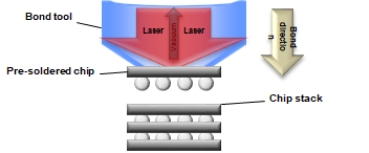

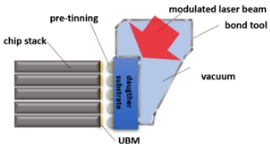

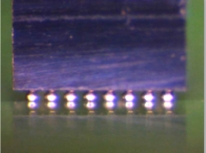

垂直実装用装置:LAPLACE-VC

コンセプトとアプリケーション

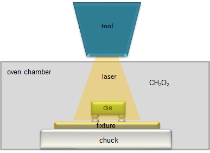

LAPLACEのカスタム対応

アプリケーション

- ギ酸(Formin acid)によりフラックスレス実装可能

- 様々な雰囲気設定が可能(活性ガス、不活性ガス、真空 など)

- セルフアライメントにより高い実装精度が可能

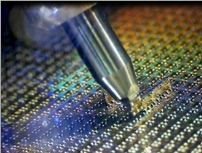

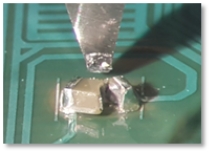

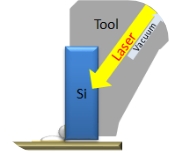

LAPLACEのカスタム対応

- Capillaryでピンを固定

- Solder上のピンを直接Laserで加熱

- Capillaryの隙間からN2ガスを断続的に供給

- フラックスレス実装